8089 I/O Processor

The Intel 8089 input/output co-processor was available for use with the 8086/8088 central processor. It used the same programming technique as 8087 for input/output operations, such as transfer of data from memory to a peripheral device, and so reducing the load on the CPU.

Because IBM didn't use it in IBM PC design, it did not become well known; later I/O-co-processors did not keep the x89 designation the way math co-processors kept the x87 designation. It was used in the Apricot PC and the Intel Multibus iSBC-215 Hard disk drive controller.It was also used in the Altos 586 multi-user computer. Intel themselves used the 8089 in their reference designs (which they also commercialized) as System 86

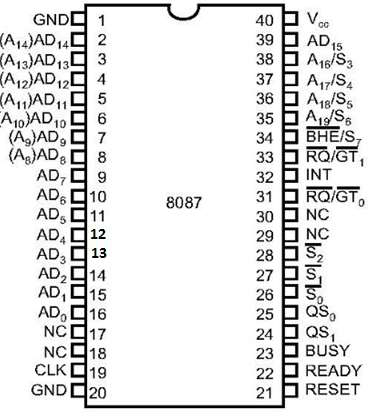

Pinout of Intel 8089

OVERVIEW

8089 is an I/O processor.

It was available for use with the 8086/8088 central processor.

It uses the same programming technique as 8087 for I/O Operations, such as transfer of data from memory to a peripheral device.

8089 has very high speed DMA capability.

It has 1 MB address capability.It is compatible with iAPX 86, 88.

It supports local mode and remote mode I/O processing.

8089 allows mixed interface of 8-and 16-bit peripherals, to 8-and 16-bit processor buses.

It supports two I/O channels.

Multibus compatible system interface.

Memory based communications with CPU.

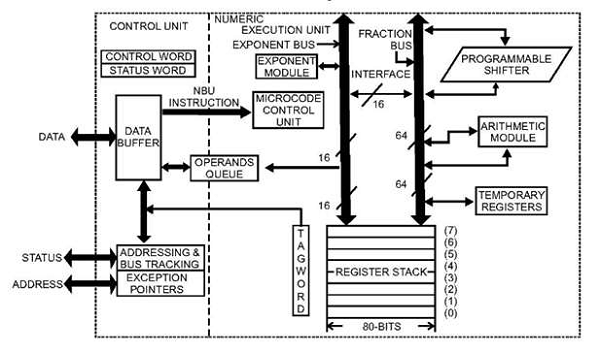

ARCHITECTURE OF 8089

I) Common Control Unit (CCU):

8089 I/O Processor has two channels.

The activities of these two channels are controlled by CCU.

CCU determines which channel—1 or 2 will execute the next cycle.

In a particular case where both the channels have equal priority, an interleave procedure is adopted in which each alternate cycle is assigned to channels 1 and 2.

II) Arithmetic & Logic Unit (ALU):

ALU is used to perform the Arithmetic & Logical operations.

It performs Arithmetic Operations like Addition, Subtraction & Logical Operations like AND, OR, EX-OR etc.

ALU looks after the branching decisions.

III) Assembly/Disassembly registers:

This registers permits 8089 to deal with 8-or 16-bit data width devices or a mix of both.

In a particular case of an 8–bit width I/O device inputting data to a 16-bit memory interface, 8089 capture two bytes from the device and then write it into the assigned memory locations with the help of assembly/disassembly register.

IV) Bus Interface Unit (BIU):

Fetch the instruction or data from primary memory.

Read / Write of data from / to primary memory.

I/O of data from / to peripheral ports.

Address generation for memory reference.

V) Instruction Fetch:

It is used to fetches the instructions from the external memory and stores them in the Queue to be executed further.

Does 8089 generate any control signals.

No, 8089 does not output control bus signals: IOW, IOR, MEMR, MEMW, DT/ R, ALE and

DEN. These signals are encoded into S0 − S2 signals, which are output pins for 8089 and

are connected to the corresponding pins of 8288 bus controller and 8289

bus arbiter to generate memory and I/O control signals. The bus controller then outputs

all the above stated control bus signals. The S0 − S2 signals are encoded as follows

These signals change during T4 if a new cycle is to be entered. The return to passive state

in T3 or TW indicates the end of a cycle. These pins float after a system reset— when the

bus is not required.

DRQ AND EXT PINS

DRQ and EXT stand for Data Request and External Terminate, both being input pins—

DRQ1 and EXT1 for channel 1 and DRQ2 and EXT2 for channel 2.

DRQ is used to initiate DMA transfer while EXT for termination of the same. A high on

DRQ1 tells 8089 that a peripheral is ready to receive/transfer data via channel 1. DRQ must

be held active (= 1) until the appropriate fetch/stroke is initiated.

programmed by the channel control register. This signal must be held active (= 1) until

termination is complete.

Utility of LOCK signal.

It is an output signal and is set via the channel control register and during the TSL instruction.

This pin floats after a system reset—when the bus is not required.

The LOCK signal is meant for the 8289 bus arbiter and when active, this output pin

prevents other processors from accessing the system buses. This is done to ensure that

the system memory is not allowed to change until the locked instructions are executed.

SINTR PIN

SINTR stands for signal interrupt. It is an output pin from 8089 and there are two such

output pin SINTR1 and SINTR2—for channel 1 and 2 respectively.

Like 8087, 8086 does not communicate with 8089 directly. Normally, this takes place via a

series of commonly accessible message blocks in system memory.

SINTR pin is another method of such communication. This output pin of 8087 can

be connected directly to the host CPU (8086) or through an 8259 interrupt controller.

A high on this pin alerts the CPU that either the task program has been completed or else

an error condition has occurred.

APPLICATIONS

File and buffer management in hard disk/floppy disk control.

Provides for soft error recovery routines and scan control.

CRT control such as cursor control and auto scrolling made simple with 8089.

Keyboard control, communication control, etc